Quartus Prime 是由 Intel(原 Altera)公司开发的一款功能强大的 FPGA(现场可编程门阵列)和 CPLD(复杂可编程逻辑器件)集成设计软件,广泛应用于数字系统设计、原型验证和嵌入式开发等领域,对于初学者而言,掌握 Quartus Prime 的基本流程和核心功能是入门的关键,本教程将详细介绍从软件安装到设计实现的完整步骤,帮助用户快速上手。

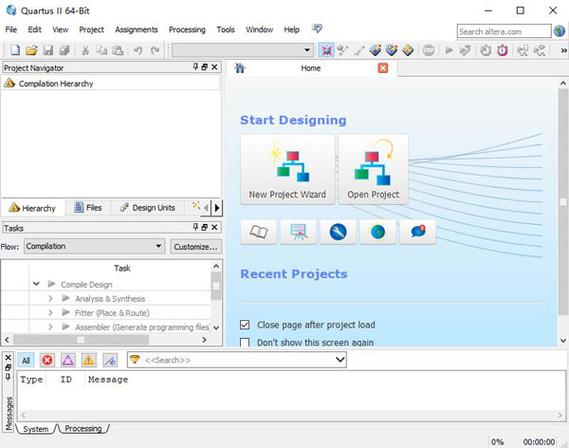

软件安装与环境配置

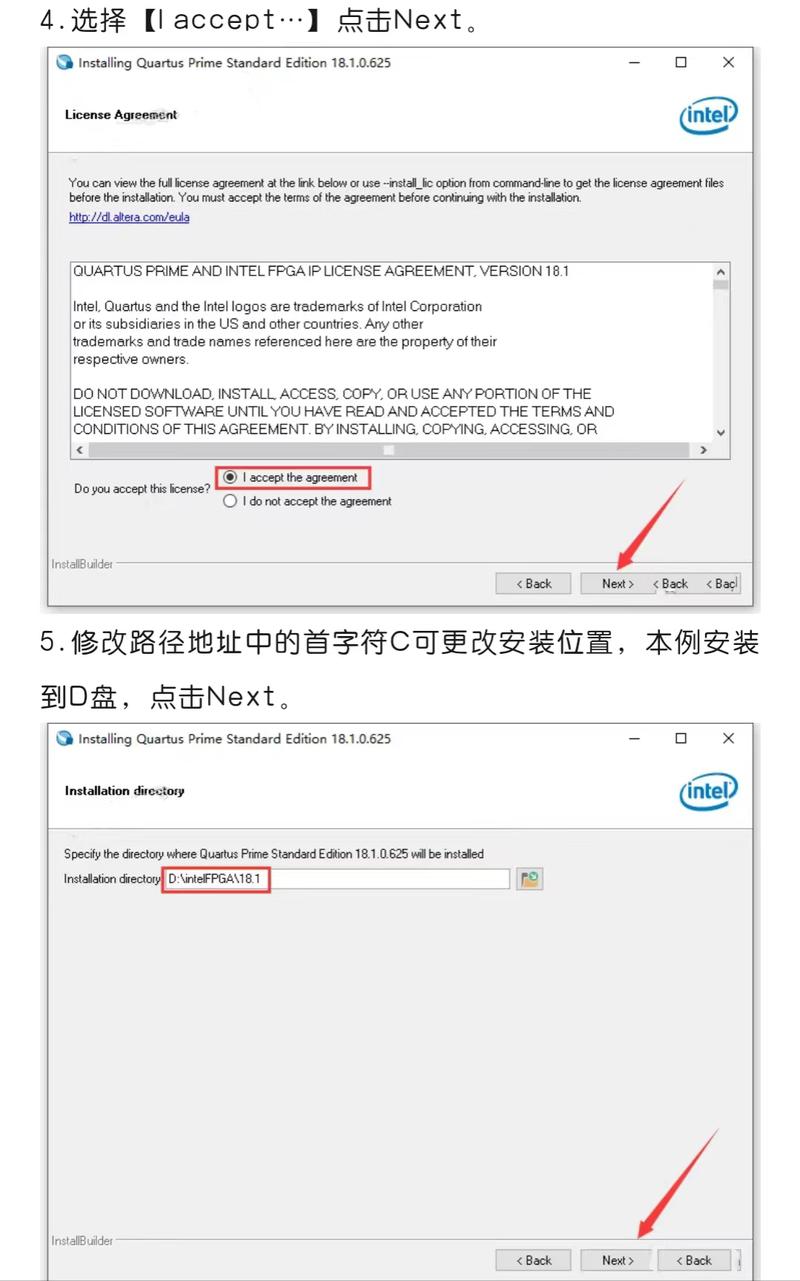

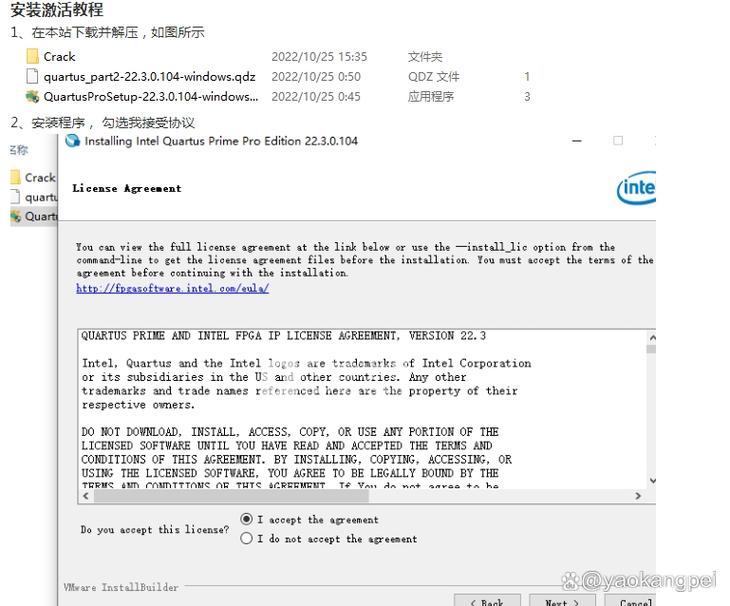

需要从 Intel 官网下载 Quartus Prime 软件的对应版本,如 Quartus Prime Standard Edition 或 Lite Edition(免费版),下载完成后,运行安装程序,根据向导提示选择安装路径和组件(如 ModelSim 仿真工具、SDK 开发工具等),安装完成后,启动软件,首次运行时会要求激活许可证,用户可选择免费许可证或申请商业许可证,在“Tools”菜单中设置“License Management”,将许可证文件与软件绑定,完成环境配置。

新建工程与设计输入

-

创建新工程:在 Quartus Prime 主界面中,点击“File”→“New Project Wizard”,进入工程创建向导,依次设置工程名称、保存路径、顶层设计实体名称,选择目标器件系列(如 Cyclone IV、Cyclone V 等)和具体型号(根据开发板或需求选择),在“EDA Tool Settings”中,可选择第三方仿真工具(如 ModelSim),若无特殊需求可直接跳过。

-

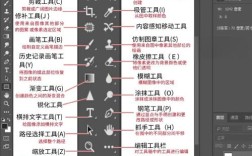

设计输入方式:Quartus Prime 支持多种设计输入方式,主要包括原理图输入、硬件描述语言(HDL)输入和 IP 核集成。

- 原理图输入:适合初学者或简单逻辑设计,通过“Block Diagram/Schematic File”创建原理图,使用工具栏中的逻辑门、连线等符号绘制电路。

- HDL 输入:主流设计方式,支持 Verilog HDL 和 VHDL,点击“File”→“New”,选择“Verilog HDL File”或“VHDL File”,编写代码并保存。

- IP 核集成:在“Tools”→“IP Catalog”中搜索所需 IP(如 FIFO、PLL、DDR 控制器等),配置参数后生成 IP 模块,可直接添加到工程中。

设计分析与综合

完成设计输入后,需对代码进行分析和综合,点击“Processing”→“Start Compilation”,软件会自动完成以下步骤:

- 设计分析:检查语法错误、端口匹配等,若存在错误,会在“Messages”窗口显示提示信息。

- 逻辑综合:将 HDL 代码或原理图转换为与目标器件相关的逻辑网表(.db 文件)。

- 适配:将综合后的网表映射到目标器件的硬件资源(如 LUT、FF、BRAM 等)。

编译过程中可通过“Compilation Report”查看资源占用情况(如逻辑单元数量、存储器使用率)、时序分析结果等关键信息。

功能与时序仿真

仿真验证是确保设计正确性的重要环节,分为功能仿真(不考虑时序)和时序仿真(包含布局布线后的延迟)。

-

功能仿真:

- 创建波形文件:点击“File”→“New”→“Vector Waveform File”,设置仿真时间,添加输入/输出节点并初始化信号。

- 运行仿真:在“Tools”→“Run Simulation Tool”中选择“Functional Simulation”,软件调用 ModelSim 等工具生成波形,观察输出是否符合预期逻辑。

-

时序仿真:

完成全编译后,在“Run Simulation Tool”中选择“Timing Simulation”,仿真结果会包含器件内部延迟,可验证设计在真实时钟频率下的稳定性。 (图片来源网络,侵删)

(图片来源网络,侵删)

引脚分配与编程下载

-

引脚分配:

点击“Assignments”→“Pin Planner”,在弹出的界面中根据硬件原理图为设计端口分配具体的物理引脚(如时钟引脚、LED 引脚等),分配完成后需重新运行编译,生成包含引脚信息的配置文件(.sof)。 -

编程下载:

- 连接 FPGA 开发板,通过“Tools”→“Programmer”打开编程窗口。

- 添加编译生成的 .sof 文件,选择“Program/Configure”选项,点击“Start”完成下载。

- 若使用 JTAG 模式,可实时调试设计;若使用 AS 模式,可将配置文件烧录至 EPCS 存储器,实现上电自动加载。

设计优化技巧

- 时序优化:对于高速设计,可通过“TimeQuest Timing Analyzer”分析关键路径延迟,调整约束条件(如设置时钟频率、多周期约束)或优化代码结构(如减少逻辑层级)。

- 资源优化:避免使用过多组合逻辑,优先使用 IP 核或状态机实现复杂功能;通过“Settings”中的“Analysis & Synthesis Settings”调整综合策略(如平衡面积与速度)。

- 增量编译:对于大型设计,启用“Incremental Compilation”可仅重新编译修改部分,缩短编译时间。

常见问题与解决方案

-

编译报错“Error (12025): Node cannot be fitted”:

原因:目标器件资源不足或引脚分配冲突。

解决:检查资源占用报告,更换更大容量器件或优化设计;检查 Pin Planner 中是否有重复引脚分配。 -

仿真结果与设计不符:

原因:测试激励不完整或忽略器件初始化特性。

解决:补充测试用例,添加复位信号确保电路初始状态正确;检查 HDL 代码中是否存在隐存的锁存器。

相关问答 FAQs

Q1:Quartus Prime Lite Edition 与 Standard Edition 有何区别?

A1:Quartus Prime Lite Edition 是免费版本,支持部分 Intel FPGA 器件(如 Cyclone IV、Cyclone V 系列),功能受限(如不支持高级时序分析工具);Standard Edition 为商业版本,支持全部器件系列,并提供完整的 IP 核库、时序优化工具和技术支持。

Q2:如何在 Quartus Prime 中使用第三方仿真工具(如 ModelSim-Altera)?

A2:首先安装 Modelsim-Altera 版本,在 Quartus Prime 中通过“Tools”→“Options”→“EDA Tool Settings”设置 Modelsim 的安装路径;创建工程时,在“EDA Tool Settings”中选择“Simulation”并指定 Modelsim 为仿真工具;编译完成后,可直接通过“Run Simulation Tool”调用 Modelsim 进行仿真。